2 S Complement Adder Subtractor Circuit. I am taking a modern digital design course and i am stuck on our lab for this week. The 2 s complement adder subtractor using one inverter adder was constructed in this paper which add sub 1 have less area delay and cost consumption compared conventional 1 bit full adder element.

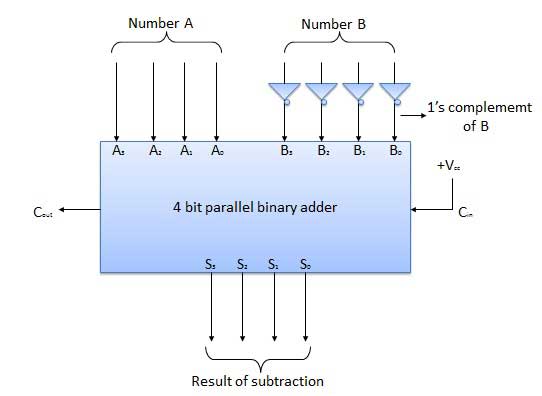

The circuit must be connected through a 4 bit adder then connected through a bcd 7 segment converter and displayed on a 7 segment display. It shows how we can use a parallel adder to design a circuit which is capable of performing. Adding b to a is equivalent to subtracting b from a so the ability to add negative numbers implies the ability to do subtraction.

A 4 bit ripple carry adder subtractor based on a 4 bit adder that performs two s complement on a when d 1 to yield s b a.

Adding b to a is equivalent to subtracting b from a so the ability to add negative numbers implies the ability to do subtraction. A 4 bit ripple carry adder subtractor based on a 4 bit adder that performs two s complement on a when d 1 to yield s b a. Basic theory related to 2 s complement adder subtractor unit. In this paper the 2s complement adder design with overflow was implemented as first time in qca have the smallest area with the least number of cells reduced latency and low cost achieved with one inverter reduced full adder using majority logic.