Negative Edge Triggered D Flip Flop Circuit Diagram. The enable signal is renamed to be the clock signal. A timing diagram illustrating the action of a positive edge triggered device is shown in fig.

Level triggered flip flops. Jk flip flop can either be triggered upon the leading edge of the clock or on its trailing edge and hence can either be positive or negative edge triggered respectively. A timing diagram illustrating the action of a positive edge triggered device is shown in fig.

Project access type.

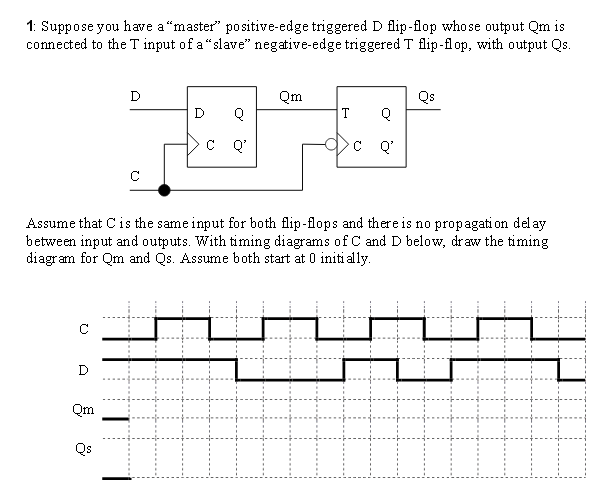

Whenever we enable a multivibrator circuit on the transitional edge of a square wave enable signal we call it a flip flop instead of a latch. Thus the output has two stable states based on the inputs which have been discussed below. Jk flip flop circuit in order to have an insight over the working of jk flip flop it has to be realized in terms of basic gates similar to that in figure 2 which expresses. Negative edge triggered flip flop.