Positive Edge Triggered D Flip Flop Timing Diagram. Jk flip flop can either be triggered upon the leading edge of the clock or on its trailing edge and hence can either be positive or negative edge triggered respectively. J corresponds to a set signal and k corresponds to a reset signal.

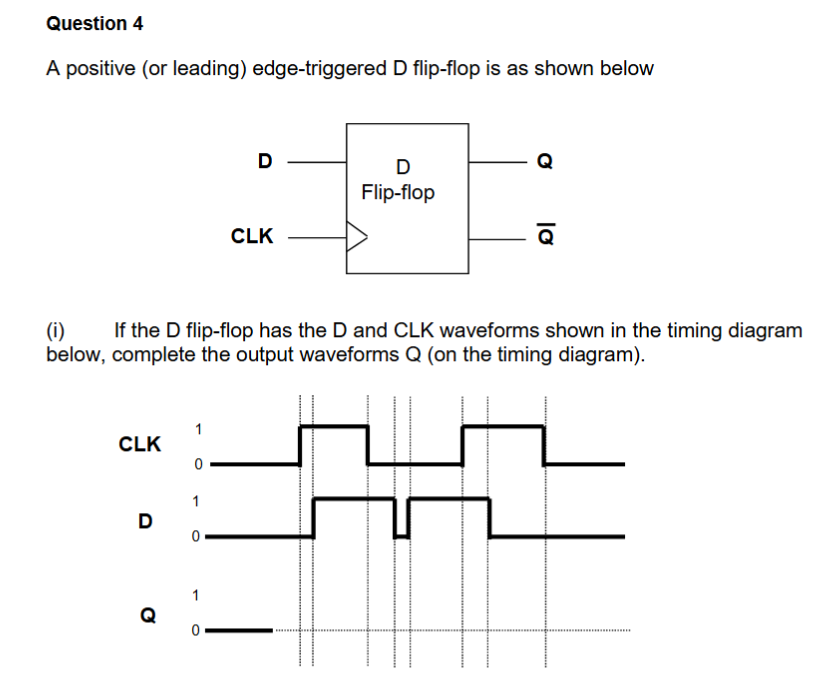

Read input only on edge of clock cycle positive or negative example below. Consequently and edge triggered s r circuit is more properly known as an s r flip flop and an edge triggered d circuit as a d flip flop. Truth table of d flip flop.

That s why it is commonly known as a delay flip flop.

Jk flip flop can either be triggered upon the leading edge of the clock or on its trailing edge and hence can either be positive or negative edge triggered respectively. Whenever we enable a multivibrator circuit on the transitional edge of a square wave enable signal we call it a flip flop instead of a latch. D c s c r d clock q q. Consequently and edge triggered s r circuit is more properly known as an s r flip flop and an edge triggered d circuit as a d flip flop.