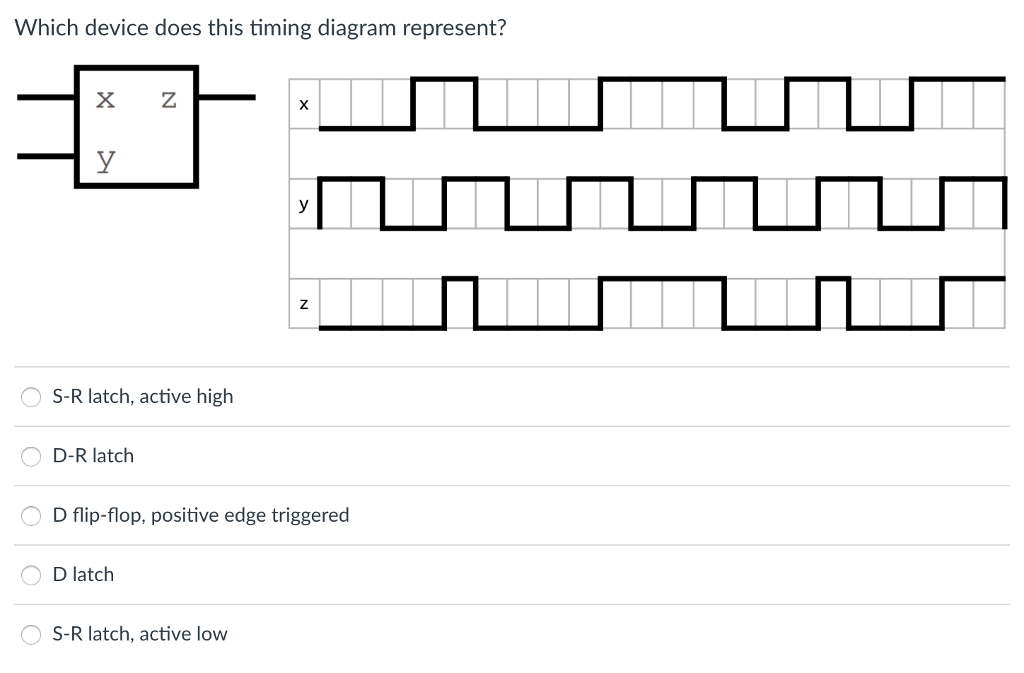

Timing Diagram Of Sr Flip Flop. Read input while clock is 1 change output when the clock goes to 0. In the first timing diagram when s becomes 1 after 10ns qn becomes 0 and 10ns later q becomes 1.

The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. Sr flip flop is the simplest type of flip flops. The clocked sr flip flop fig.

Sr flip flop is the simplest type of flip flops.

Now draw the s r latch with nor gates write initial values near corresponding letters s 0 r 0 q 0 qn 1 change s to 1 and try to understand what changes you see. Sr flip flop is the simplest type of flip flops. The clocked sr flip flop fig. Sr flip flop construction logic circuit diagram logic symbol truth table characteristic equation excitation table are discussed.